摘要

随着对更高效、更紧凑的电⼒电⼦器件的需求不断增⻓,半导体⾏业正在利用硅(Si) 的替代品,包括宽禁带(WBG)材料,如碳化硅(SiC)和氮化镓(GaN)。高电⼦迁移率晶体管(HEMT)配置中的GaN具有效率和速度优势。然而,它们需要改进传统的基于硅的测试和特性分析⽅法。

精心设计GaN器件和封装,以及进⾏热特性和可靠性测试,对于确保其在现场应用中的最佳性能和耐用性至关重要。

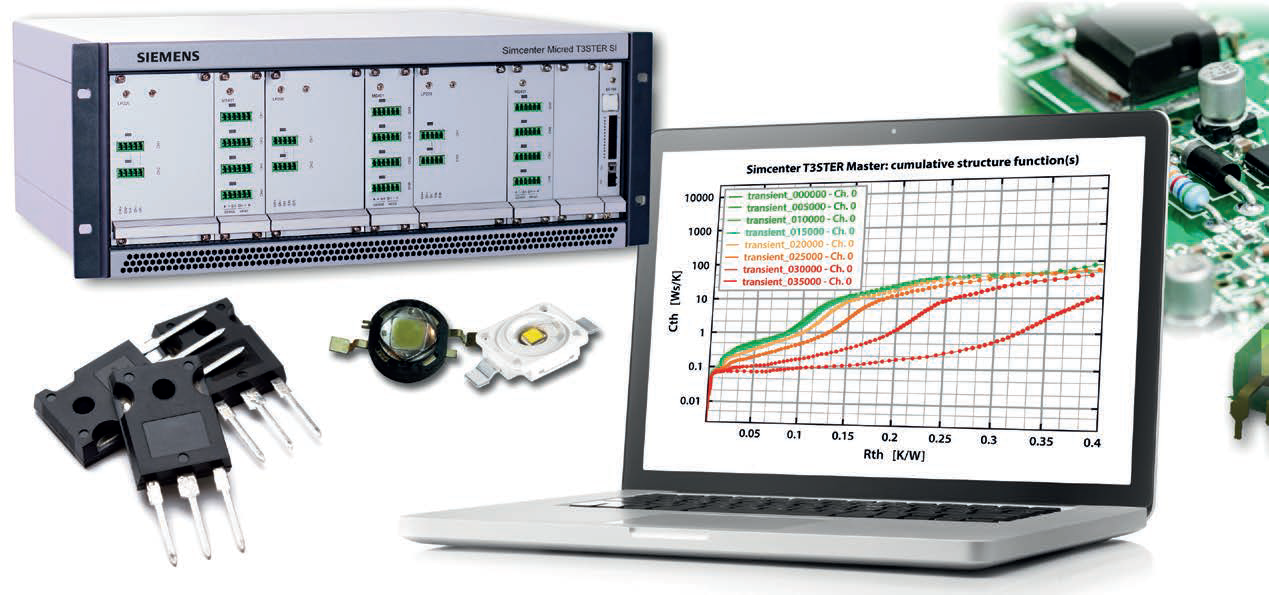

因此,使用Simcenter Micred硬件和软件,这也是西门⼦Xcelerator业务平台的一部分,该平台包括用于热性能和可靠性测试的硬件、硬件和服务,有助于确保高功率密度电⼒电⼦应用中的最佳热管理和可靠性。

内容

1.介绍

2.热特性概述

3.基本FET操作和瞬态热测试

3-1 对使用FET作为电子开关的回顾分析

3-2 场效应器件的瞬态热测试的方法

4.GaN材料上的HEMT

5.GaN HEMT瞬态热测试挑战和解决⽅案

5-1 通过沟道电阻进行加热和测试的瞬态热测试方法

5-2 通过栅极肖特基二极管进行测试的瞬态热测试方法

5-3 通过栅极漏电流进行测试的瞬态热测试方法

5-4 对共源共栅Cascode HEMT器件进行瞬态热测试

6.结论

7.参考书目

1.介绍

电力电子技术主要基于硅基材料制造的半导体器件。然而,近年来,这些硅器件已经达到了极限。因此,电力电子技术可以通过利用新的半导体材料来改进[1]。

在过去的20年里,SiC和GaN等WBG半导体材料因其良好的电学和热学特性而受到特别关注。

在许多应用中,SiC金属氧化物半导体场效应晶体管(MOSFET)取代了标准的硅的绝缘栅双极型晶体管(IGBT)和⼆极管,因为它们效率更高,同时保持了标准栅极控制。因此,很容易将现有的电路控制⽅案适应于这种材料[1]。

基于GaN的优越材料特性,可以实现具有显著更高运行速度和改进击穿特性的新应用。然而,与SiC器件相比,GaN功率器件在开发和标准化方面仍落后几步。这使得工程师由于不熟悉它们而难以将它们集成到新的电源应用中。为了充分利用GaN器件的优势,开发新颖的构造原理和复杂的测试技术非常重要[2]。

因此,可以预见,未来GaN器件市场将蓬勃发展。与过去几十年来Si技术⽇趋成熟的艰苦努⼒相似,当代研究人员和⾏业领导者继续应对GaN技术挑战,旨在充分发挥其在下一代电⼒电⼦领域的潜⼒。

西门子数字工业软件致力于开发符合前沿应用的新测试技术和仿真方法。本白皮书重点介绍GaN功率器件的热测试。

此外,由于用户对晶体管等经典半导体器件的结构和操作有了基本的了解,因此下面参考资料部分中的科学论文对这些主题提供了更深入的见解[2] [3]。

2.热特性概述

为了确保最佳性能和耐用性,必须精心设计GaN器件和封装,并扩展其在热领域的测试。它们独特的电气特性需要开发创新的热测试⽅法。使用Simcenter Micred系列产品是这一演变的前沿,可以开创应对这些挑战的⽅法[4]。

利用Simcenter Micred解决⽅案可以高效地测试、测量和表征集成电路(IC)封装、电⼒电⼦器件和完整电⼦系统的热性能。结温(Tj)是这些测试中的一个关键指标,在经过细致微调的封装的热阻(Rth)和优化其在高温条件下的性能⽅面起着至关重要的作用。

Micred解决方案中实施的测试方法在JESD51-1[5]中有定义。半导体器件用作基于校准的温度敏感参数(TSP)的温度传感器。对器件施加功率阶跃会引起瞬态热响应。准确测量结温的热瞬态变化可以建立瞬态热阻抗曲线,进而获得结构函数曲线。现有的热测试标准,例如JEDEC JESD51系列,定义了传统硅器件的电气测试方法。将该方法扩展到WBG器件需要彻底地重新考虑。

图1:Simcenter Micred瞬态热测试解决⽅案

3.基本FET操作和瞬态热测试

半导体行业已引入多种类型的器件用于功率应用。这些器件的典型用途是高频放大。另外,其它的器件可用于开关目的,包括可控硅整流器(SCR)或晶闸管、双极结型晶体管(BJT)、场效应晶体管(FET)和IGBT,后者是MOSFET器件和BJT器件的结合。

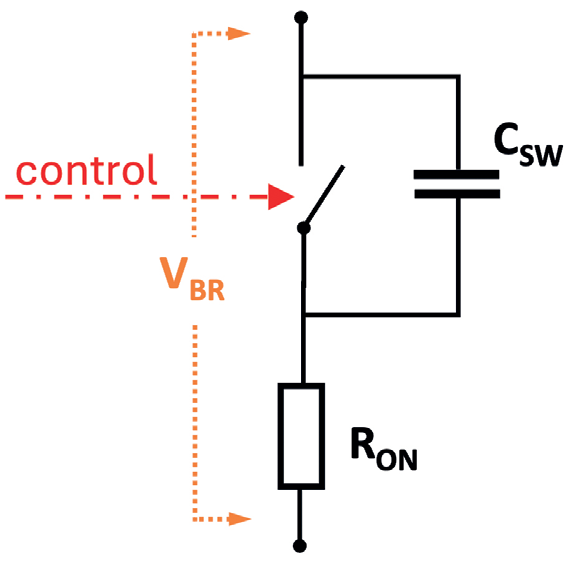

图2描绘了半导体开关的通用⽅案,强调了其⾮理想特性。

图2:半导体开关的等效电路图

导通时,半导体器件的导通电阻(Rdson)会导致在器件产生压降,从而产⽣导通损耗。此外,寄⽣频率相关电容(Csw)的充电和放电过程也会导致开关损耗。另外,击穿电压(VBR)限制了器件在不损坏的情况下可以阻断的最大电压。

控制开关发生在半导体器件的另一个引脚上,最好是在低电压和低电流下进行。

在放大和调制应用中,器件以调制电阻持续导通。

这些功率器件的热测试需要半导体中的加热部分和温度传感器结构。上述通用方案指出了与导通和开关损耗相关的可能加热效应,但并未直接提供固有的芯片温度传感器。实际应用通常缺乏专用的温度传感器;但是,一些额外的半导体结构,如寄生PN结,可用于此目的。

3-1对使用FET作为电子开关的回顾分析

对应图2,半导体开关具有永久导电域,这些域由外部电信号控制的部分区分开,以处于导电状态和绝缘状态。

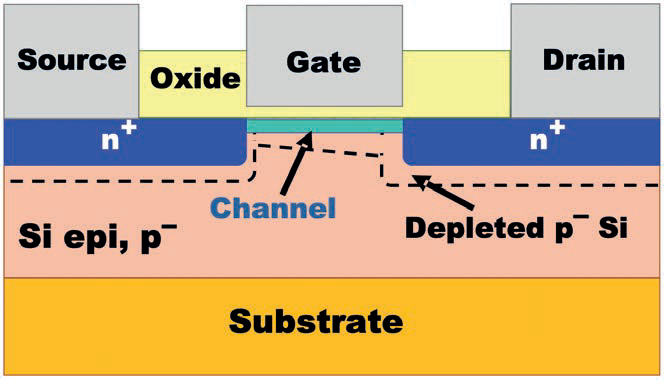

为了了解GaN场效应器件的当前和未来的构造和用途,值得总结和重述最常见的FET,即金属氧化物半导体结构(n型MOSFET)的运行,如图3所示。

图3:横向n型MOSFET的层结构

图4:图3中的MOS结构中的结,包括PN同质结和欧姆结或肖特基结

在这些器件中,源极和漏极区域采用强n+掺杂制造,将自由移动的电子释放到各自的域中。

在薄栅极氧化物下面,可能会发生几种情况。20世纪60年代初期,硅和石英晶格的不匹配导致大量悬空硅键,代表着大量正电荷。当即使栅极电压为零时,该电荷会吸引大量可移动的负电荷载流子,从而在漏极和源极之间形成导电沟道。

因此,当时所有n型晶体管都是常开、耗尽型。需要足够高的负栅极电压来排斥电子并在栅极下方形成耗尽层,从而完全隔离漏极和源极。所有这些MOSFET通常都是常开、耗尽型器件。

由于静态功耗、电路设计的简化和安全问题,常闭、增强操作的晶体管是首选。制造商通过对MOSFET技术进行几项改进逐渐开发了这些晶体管。

出现导电沟道时的特征栅源电压(Vgs)表示为阈值电压(Vth)。在较高的Vgs下,导电沟道变厚,而占漏极和源极之间总(Rdson)最大部分的沟道电阻会减小。

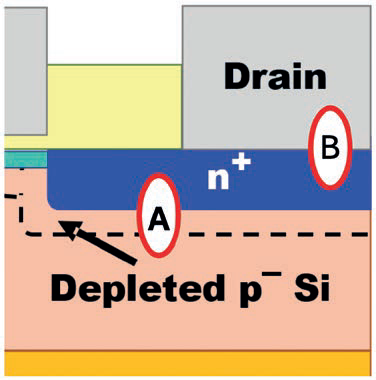

图4是图3的部分放大。在横截面视图中,我们可以观察到两个结。结A是n+漏极和 p层之间的PN结;后者连接到硅衬底。

接触金属条与n+区域的界面处的结B确保电流进入半导体。两种材料之间的接触电位决定了结的行为。最佳情况下,该结是欧姆接触。根据金属成分和n+掺杂,这两种材料可以形成具有薄耗尽区的肖特基结。在这种情况下,该技术旨在将其正向电压(Vf)保持在较低水平,即使在高电流下也是如此。

图3和图4描绘了在半导体表面上构建的横向MOS器件。物理上的功率MOS结构是垂直排列的,生长到晶体结构中[3] [7]。

3-2场效应器件的瞬态热测试

在瞬态热测试中,被测器件(DUT)在两个功率水平之间切换,并且必须及时记录温度敏感参数随时间的变化关系。在瞬态热测试中测量冷却曲线是首选,因为它可以避免加热期间的功率变化问题,简化低功率级下的校准并降低计算复杂性[8]。

正如文献中广泛解释的那样,例如参考文献四,所有半导体结构都可以充当温度敏感参数[4]。

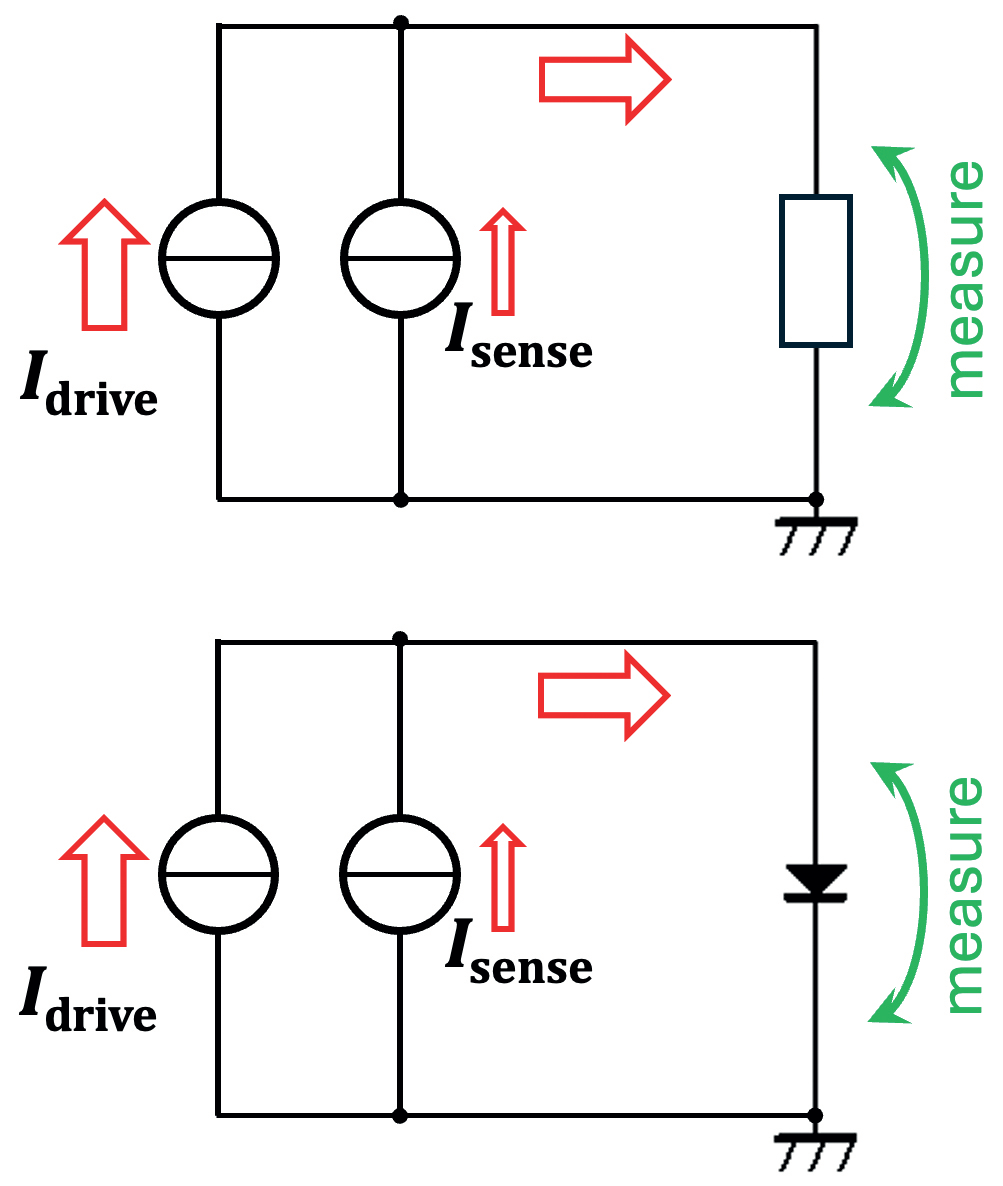

在多个测试标准中[5],瞬态热测试概念是针对双引脚被测器件定义的,如图5所示。在这种方法中,被测器件被简化为电阻器或结,同时充当加热器和传感器。

图5:半导体器件的基本热测试方案,包括电阻型(上图)器件和结型(下图)器件

大的加热电流Idrive流过电阻或结会使被测器件发热。关闭加热电流Idrive后,在冷却期间被测器件上仍会保持小的测试电流Isense;器件两端的电压充当温度敏感参数TSP。

半导体器件的结具有负的温度敏感参数。阻性半导体域也可能具有正的温度敏感参数,具体取决于技术参数。例如,硅的MOSFET中的导电沟道可以充当具有正的温度敏感参数的电阻。

对于三引脚器件的功率晶体管,有更多可能性可以产生功率变化。

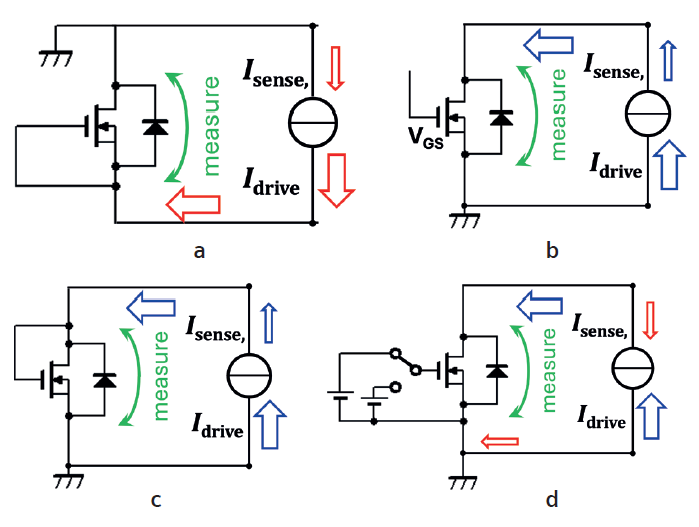

图6:MOSFET 器件的热瞬态测量方案:

a)反向二极管作为加热器和传感器;

b)具有受控栅极电压的MOSFET;

c)MOS二极管设置,漏极连接到栅极;

d)加热在沟道上,测量在反向二极管上

这些方法继承了双引脚测量的优点和缺点。器件的有源特性决定了强制电流下的功率水平。

图6a的示意图与器件的实际使用情况不太接近,加热和测试发生在MOSFET的反向二极管(结A)。功率是有限的;它是Vf正向电压和正向电流(IF = Idrive + Isense)的乘积。尽管如此,结在施加小的测试电流Isense情况下提供清晰且无噪声的瞬态响应,从而实现高保真度评估。

图6b的示意图显示了沟通上的加热和测试,正确模拟了实际使用情况下的功率耗散。然而,这提供了低信号电平,特别是在具有低沟道电阻的器件中。此外,初始寄生电效应可以在与热瞬态相同的时间域中产生具有相当或更高幅度的寄生电瞬态,从而严重扭曲温度信号。

图6c的示意图显示了MOS-Diode的测量布置,漏极在加热和冷却期间连接到栅极,器件上的电压高于Vth。TSP是该阈值电压的温度依赖特性。由于具有升高的电压,这种测量布置可以在降低的电流水平下提供高耗散功率,但由此产生的工作点可能导致芯片表面温度分布不均匀,从而导致某些器件种类在加热期间出现稳定性问题。

图6d显示了沟通上的加热和反向二极管上的测量,将描述实际应用的加热方案与反向二极管的高的温度敏感度相结合。因此,它是测量指南的首选方法[9]。可以观察到开关元素用于加热,分析实际应用中的劣化机制,并使用寄生结构(结A)作为温度敏感参数。此概念可以成功转移到MOS结构以外的其他器件类型。

注:所有测试方法都基于对Vgs栅极源电压的适当控制。

4.GaN材料上的HEMT

要讨论如何调整基于GaN的器件的瞬态热测试,了解这些器件结构的特性非常重要。

GaN是一种半导体材料,其中等量的镓和氮原子形成晶体。在GaN材料中,电子通过强共价键与晶格结合。当电子被外部能量,例如热量、电场或另一个电子的撞击,从共价键中撕裂时,电子可以在晶体中自由移动。要将电子从共价键中释放出来,需要带隙能量。在硅中,带隙约为1.1电子伏特(eV),在GaN中为3.4eV,使其成为一种耐高温、高电压和高电流密度的坚固材料。

在氮化铝(AlN)的类似晶体结构中,带隙约为6eV,在室温下为绝缘体。由于镓和铝的化学性质非常相似,因此可以生产铝-镓-氮化物复合半导体(AlGaN),用铝代替某些镓原子。在AlGaN中,有效带隙可以通过化合物中铝的百分比来调节。

GaN器件正在成为消费电子、光伏和车载充电器的主流,未来有望取得重大进展。目前,可以在GaN上实现具有高速和低Rdson沟通电阻的场效应晶体管。

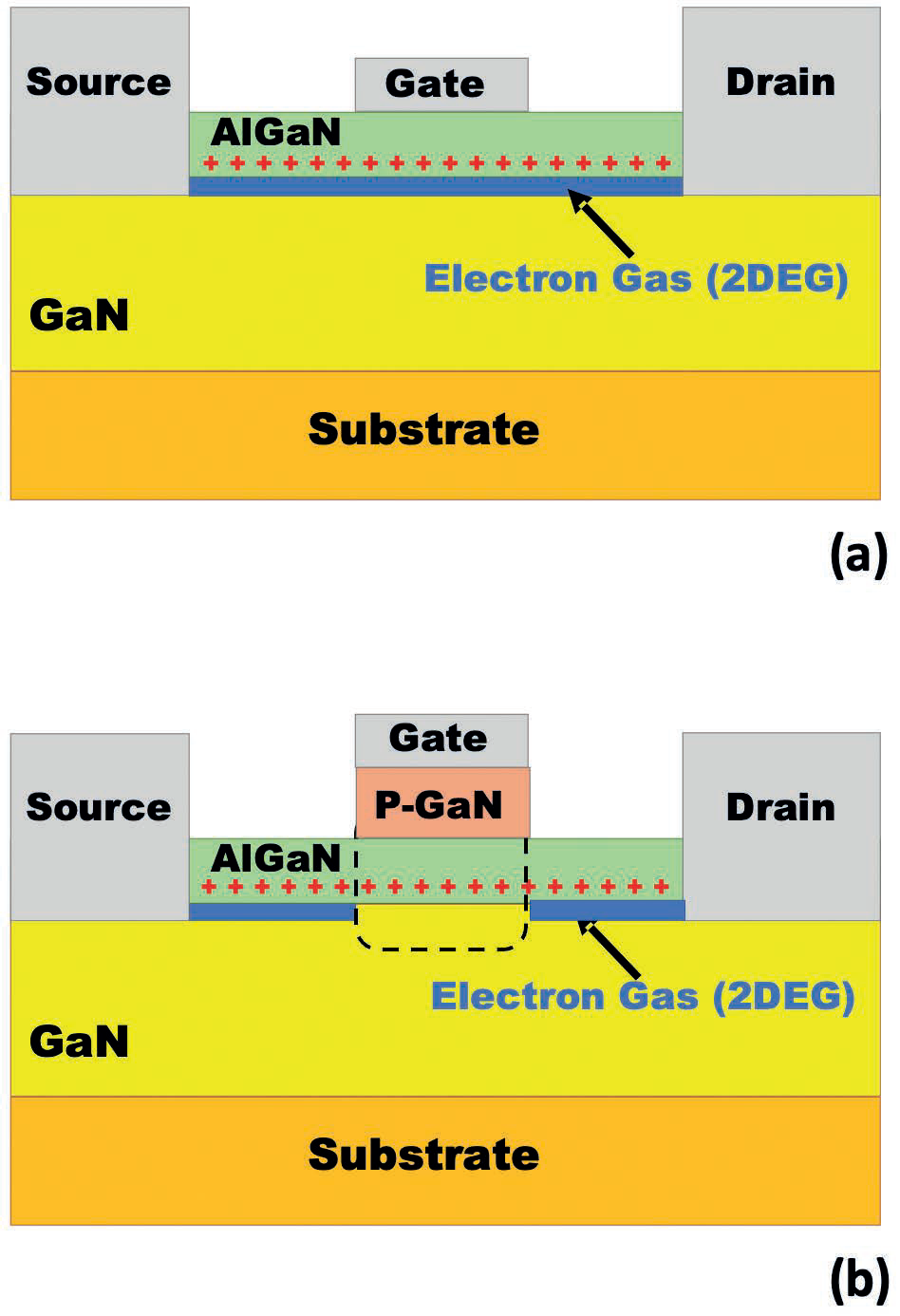

图7a显示了这些HEMT的简化形式,对应于芯片表面的横向结构,这是目前GaN功率器件的普遍形式。

图7:GaN HEMT器件的结构层次:

a)具有金属-AlGaN-GaN结构的常开器件;

b)具有金属-pGaN-AlGaN-GaN结构的常闭器件;虚线表示耗尽层的极限

在这个结构中,AlGaN层生长在单晶GaN的顶部。与之前的MOS示例类似,在两种材料的界面处会形成表面电荷,在AlGaN层中留下不可移动的固定正离子化原子,而在GaN基底中靠近界面的浅表面层中留下自由移动的电子。

AlGaN晶体层非常薄,只有几排原子。薄晶格被“紧贴“在体积更大的GaN上,因此材料之间不会发生晶格失配,从而导致“失配”的共价键。此外,没有掺杂阻碍电子的运动,因此即使存在极薄的自由可移动载流子层也能确保适当的沟道电导率。这些有利的品质证明了该器件的名称,即高电子迁移率晶体管和将浅表面电荷描述为电子气的合理性。

注:在更严格的物理处理中,这些效应被描述为异质结处具有各种带隙层的扭曲带隙结构,从而产生2维电子气(2DEG)[11]。

这些HEMT在栅极和源极之间的零电压下导电,即常开耗尽模式器件。

几种创新的设计方法导致将GaN HEMT变成常闭增强模式器件,以便在电源开关应用中实现更简单的驱动电路。

为此,广泛使用了两种类似的方法,第一种即在栅极金属化下插入受体掺杂的p型层(p-GaN),如图7b和图8。

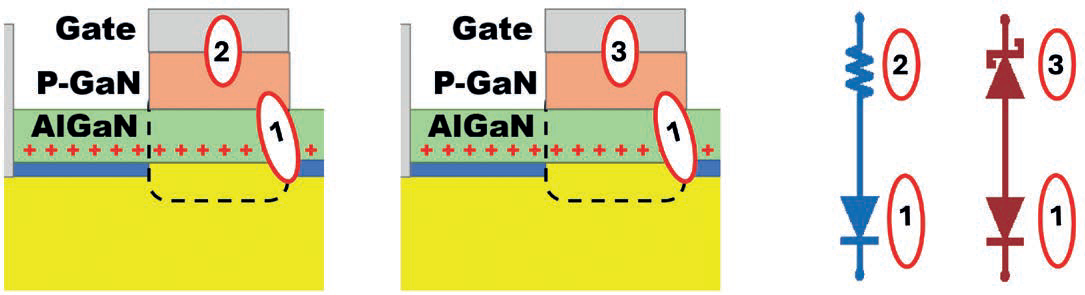

图8:(栅极、p-GaN、AlGaN、基极GaN)结构中的结和等效电路图;

PIN结构表示为1,欧姆结表示为2,反向肖特基结表示为3;

虚线表示耗尽层的极限

p-GaN层在栅极至衬底结构中插入了两个额外的材料界面或结。由于AlGaN层非常薄,只有几行原子,当接触电位在p-GaN层和GaN基极之间形成耗尽区时,未掺杂的AIGaN层会以其整个宽度落入该耗尽区,如图8下方排列中的1所示。在参考文献 11中,这表示为由pGaN-AlGaN-GaN基极层创建的PIN二极管。

在上结处,栅极金属和p-GaN之间的接触电位可以积累电荷载流子;因此,结具有欧姆性质,在图8中用2表示。这些器件通常称为栅极注入晶体管(GIT)。栅极电压调节基极GaN耗尽区的厚度。GIT器件有三种不同的操作模式:

1. 当沟道消失时,在低栅极电压下阻断;

2. 当沟道出现,但PIN二极管两端的电压保持在开启电压以下时,为经典场效应操作(对于WBG材料,高于2伏);

3. 当PIN二极管开启并向沟道注入更多电荷载流子时,为栅极电流模式;

该器件的操作类似于经典结型场效应晶体管(JFET)器件的操作。

当上结处栅极金属和p-GaN之间的接触电位耗尽p-GaN侧时,它形成反向肖特基二极管(用3表示)。这些被称为反向肖特基栅极HEMT、肖特基栅极HEMT或p-GaN 栅极HEMT。为了简单起见,下面我们称这些为SGD器件,指的是肖特基栅极结构。在不同的但核心等效的物理方法中,我们可以将常闭操作归因于肖特基结的附加接触电位、耗尽的p-GaN中电离受体原子的存储的负电荷或p-GaN层中带隙的扭曲。

GIT栅极是非绝缘的,因此由于栅极和沟道之间等效二极管的自钳位特性而具有抗过压能力。然而,阈值电压只有几伏,这是由PIN二极管决定的。SGD结构由背对背二极管半隔离,防止大量电流流动以模拟传统MOSFET栅极。

实现常闭操作同时保留GaN HEMT器件部分优点的另一种方法是将常闭、低压Si MOSFET与常开GaN HEMT器件组合在一起,采用通用封装共源共栅Cascode结构[12]。这种组合兼具两种器件的优点,即GaN HEMT的高压阻断能力和Si MOSFET的增强模式操作。

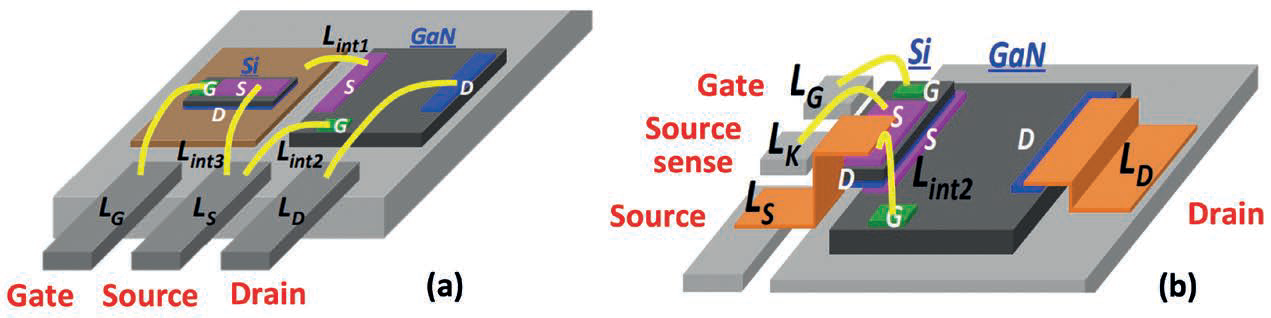

图9:共源共栅Cascode GaN HEMT器件的封装配置:(a)横向配置和(b)堆叠芯片

供应商生产各种封装配置,横向和堆叠,如图9所示。在横向配置中,芯片并排组装,而在堆叠芯片中,它们垂直安装,其中较低耗散的Si芯片位于GaN芯片上方。

5.GaN HEMT瞬态热测试挑战和解决方案

比较MOSFET和HEMT结构,我们可以从图6中的瞬态热测试设置中推断出,可以根据Rdson沟道电阻的温度依赖性,或图8中表示为1的寄生结的温度依赖性参数,来调整某些方法。

5-1通过沟道电阻进行加热和测试的瞬态热测试方法

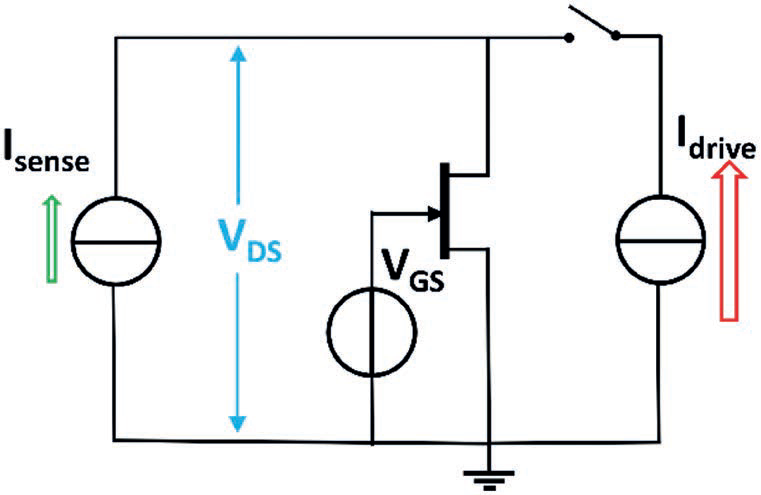

图10提供了瞬态热测试的示意图,其中加热和测量导电沟道。

图10:一个瞬态热测试的方案,在沟道上加热和测量

该方法的一个优点是所有HEMT类型中都存在沟道。但是,Rdson在现有器件中已经很低了。因此,这需要较高的Isense测试电流才能实现足够高的Vds电压降和传统瞬态热测试设备可检测到的温度诱导变化[14][15]。此外,在测试设置中区分真正的温度相关电阻变化与外部接线可能会很麻烦。

时变效应会限制这种测量模式。例如,可移动电荷可以暂时存储在捕获能级,其随后的释放会导致寄生电瞬变,从而扭曲热响应。参考文献16中重点介绍了进一步的时变和退化相关效应。

5-2通过栅极肖特基二极管进行测试的瞬态热测试方法

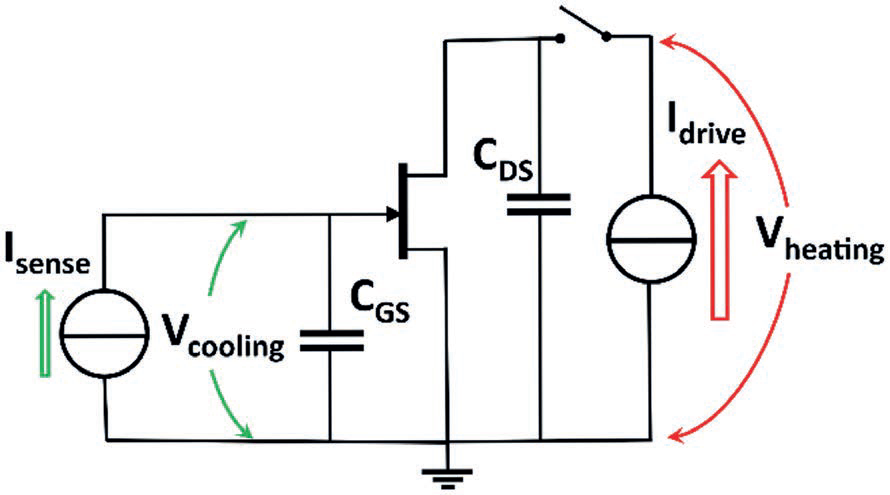

上一节中描述的经典HEMT结构和GIT类型器件变体中的栅极肖特基二极管结构可以更好地用于温度敏感参数。图11显示了测量设置。

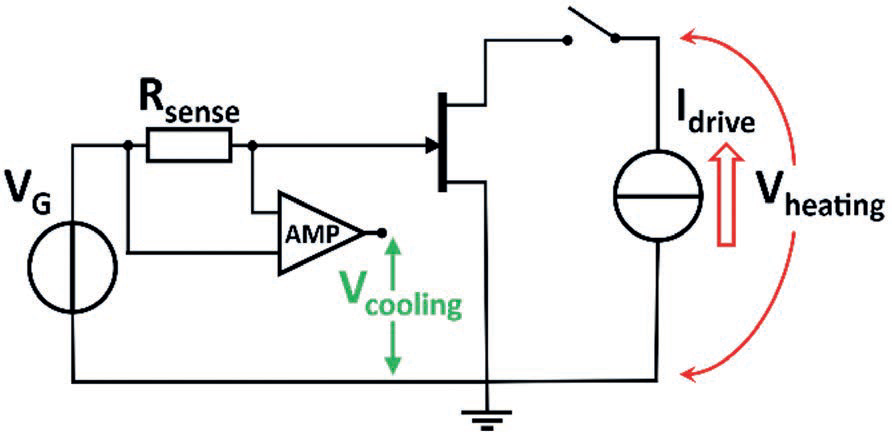

图11:一种对沟道电阻进行加热、对栅极二极管进行测试,具有连续的栅极电流的测量方案

HEMT器件,尤其是为射频(RF)放大器应用而设计的器件,可在极高频率下工作,图11所示的电路易受测量线路引起的外部寄生电感和电容的影响。为避免任何可能造成测量结果误差并损坏器件的振荡,建议在实验期间使用示波器监控测量结果,并在必要时使用适当的旁路电容器(Cgs、Cds)和铁氧体磁珠。

最大的负载电流通常受到一定限制,尤其是对于高电压RF放大器HEMT器件。因此,在之前的设置中实现的阶跃功率通常太低,无法充分加热器件,即使在最大额定电流下也是如此。

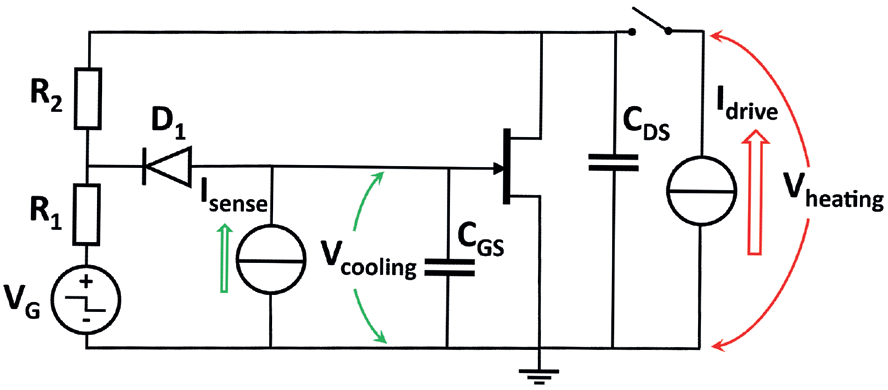

图12显示了解决这一矛盾的改进设置。Vg电压与加热电流同步在两个预设置的电压电平之间切换。在加热过程中,Vg被编程为负值,以将栅极拉至适当的负电压,从而产生更薄的通道和更高的Vds。

图12:采用升高的电压进行加热,具有开关的栅极电流的测量方案

在冷却阶段,Vg被编程为正电压。二极管D1反向偏置;因此,电压源对栅极-源极电压没有影响。测试电流Isense可以流过栅极二极管。

案例分析:

在此示例中,在RF功率GaN HEMT器件,型号为CGH40025F来自Wolfspeed上,使用连续和开关栅极电流执行了这些类型的瞬态热测试。测试使用了Simcenter Micred T3STER™ SI测试硬件,并利用Simcenter Micred T3STER Master软件显示、分析和后处理结果。

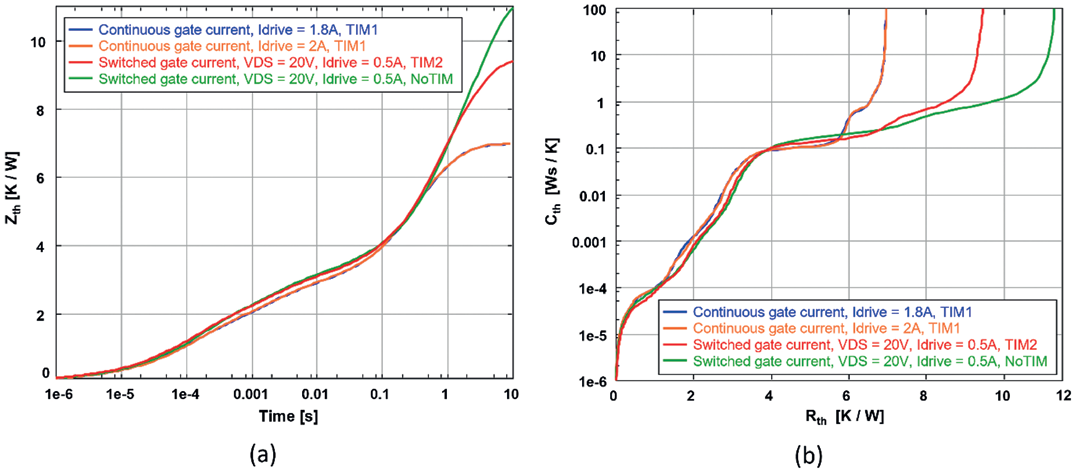

图13:CGH40025F HEMT的测量结果,具有连续和开关栅极电流,有和没有热学界面材料(TIM)、Zth曲线和结构函数

图13a显示了瞬态热阻抗曲线Zth,即通过施加的加热功率归一化的结瞬态响应。图13b显示了结构函数,即沿着从结到环境的热流路径的热阻和电容二维图。对应于两种测量模式的曲线在两种视图中都拟合得很好,直到热量传播到器件的封装内。由于器件和冷板之间的各种热界面,曲线分离仅发生在外壳表面。

5-3通过栅极漏电流进行测试的瞬态热测试方法

随着GaN HEMT器件中栅极结构的进一步发展,新设计提高了阈值电压并大幅降低了栅极漏电流。上一节中以SGD器件为例介绍了这一发展。

这使得使用栅极二极管特性在恒定电流偏置下进行的瞬态热测试技术变得不那么实用。尽管栅极具有类似二极管的I-V特性,但实际应用需要极低的测试电流,只有几十微安。这相当于源阻抗达到几十千欧姆,与瞬态热测试设备的输入电阻相当。因此,只有部分施加的测量电流流过DUT,因此无法进行恒定电流供电。

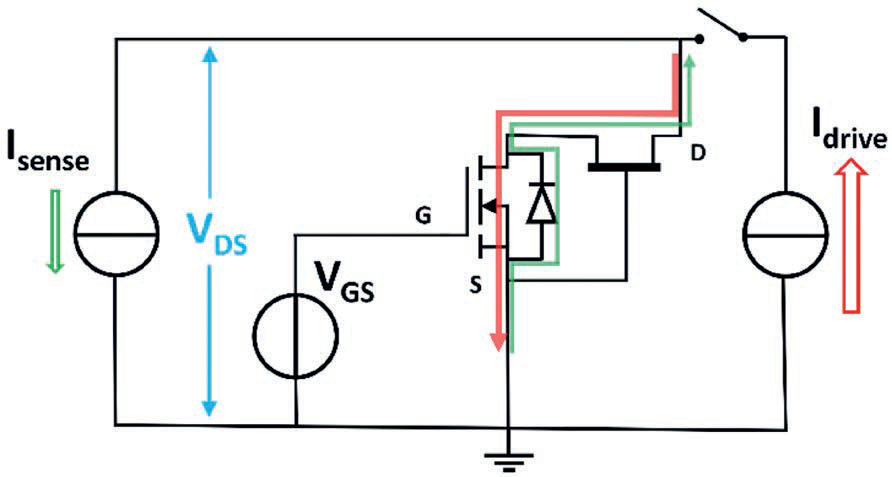

图14:HEMT测量示意图,其中对导通状态沟道电阻进行加热,并使用栅极漏电流进行温度测量

另外,除了依赖阈值电压外,栅极漏电流可用作温度敏感参数,同时保持恒定的栅极-源极电压偏置。如图14所示,此测量装置通过添加与栅极串联的适当选择的Rsense电阻,将漏电流转换为可检测的电压信号。为了在目标温度范围内实现50至100毫伏(mV)的电压降,正确调整Rsense电阻的大小非常重要。可以使用较低的电阻值来改善噪声特性,并辅以额外的信号放大器。

5-4对共源共栅Cascode HEMT器件进行瞬态热测试

在共源共栅Cascode HEMT器件中,尽管作为单个晶体管运行,但两个采用不同半导体材料的芯片组装在一个共同的封装中。每个芯片的功耗、热阻和结温也各不相同。

无论其物理实现如何,器件通常无法直接访问GaN HEMT源极和MOSFET漏极之间的连接点。这种连接对于直接测量每个芯片的热瞬变是必要的。

由于直接集成,测量堆叠芯片结构通常很简单。MOSFET芯片安装在GaN器件的顶部,两者之间的热阻较低;因此,MOSFET温度紧随HEMT温度。

图15:一种堆叠芯片共源共栅Cascode HEMT器件瞬态热测试示意图

因此,测量MOSFET器件的温度也可以近似地估算出HEMT芯片的温度。图15显示了一种可能的测量设置。更具挑战性的配置是将两个芯片并排安装。虽然两个芯片的散热可能会根据冷却条件(外壳到环境的热阻)重叠,但热耦合要弱得多。然而,表征这些器件需要复杂的热测试方法和对器件参数的额外假设。

6.结论

几十年来,硅一直主导着半导体行业。然而,随着对电力电子的需求不断发展,寻求更高的效率、紧凑的设计和极端条件下的平衡,GaN等WBG材料是有希望的候选材料。GaN HEMT配置提供了高效率和速度。然而,使用GaN HEMT的独特属性和挑战意味着,适当调整硅基器件的传统测试和特性分析方法非常重要。

GaN HEMT瞬态热测试的两个关键挑战是它们缺乏寄生体二极管和经典HEMT结构的常开操作。

建议的解决方案包括对绝缘栅HEMT使用沟道电阻Rdson,对传统的常开HEMT使用栅极肖特基测量。我们还建议使用其他测量模式,例如测量栅极漏电流和测试共源共栅Cascode HEMT器件。

正确的TSP选择可能因HEMT的结构而异。最佳方法尚未确定,可能取决于特定的器件特性,例如栅极特性或Rdson值。每个TSP都有其优点、缺点和最佳使用场景。因此,请根据具体应用选择最合适的解决方案。

7.参考书目

1. L. James. “Could silicon soon be a thing of the past?,” Power & Beyond. Accessed: Nov. 15, 2024. [Online].

Available: https://www.power-and-beyond.com/could-silicon-soon-be-a-18b2e34ad39f592ee6a1e5b-8da26febd/

2. Siemens White Paper. “Using Simcenter to fully characterize SiC devices,” Siemens Digital Industries Software.

Accessed: Nov. 15, 2024. [Online]. Available:

https://resources.sw.siemens.com/en-US/whitepaper-electronics-and-semiconductors-simcenter-forcharacterized-sic-devices/

3. G. Farkas. “Chapter 4: Temperature-dependent electrical characteristics of semiconductor devices,” in Theory and Practice of Thermal Transient Testing of Electronic Components, M. Rencz, G. Farkas, and A. Poppe, et al., Cham: Springer International Publishing, 2022,

pp. 139–169. doi: 10.1007/978-3-030-86174-2_4.

4. M. Rencz, G. Farkas and A. Poppe, et al.. Theory and Practice of Thermal Transient Testing of Electronic Components. Cham: Springer International Publishing, 2022. doi: 10.1007/978-3-030-86174-2.

5. JEDEC Standard JESD51–1, “Integrated circuit thermal measurement method - Electrical test method (single semiconductor device): | JEDEC.” Accessed: Nov. 15, 2024.

[Online]. Available: https://www.jedec.org/system/files/docs/jesd51-1.pdf

6. A. Borghese, A. Di Costanzo, M. Riccio, et al.. “Gate current in p-GaN Gate HEMTs as a channel temperature sensitive parameter: A comparative study between Schottky- and Ohmic-Gate GaN HEMTs,” Energies, vol. 14, no. 23, p. 8055, Dec. 2021, doi: 10.3390/en14238055.

7. R. Kaur. “A review on power MOSFET device structures,” Int. J. Res. Appl. Sci. Eng. Technol., vol. V, no. X, pp. 208–218, Oct. 2017, doi: 10.22214/ijraset.2017.10034.

8. G. Farkas, A. Poppe, Z. Sárkány and A. Vass-Várnai. “Chapter 6: Thermal transient measurements on various electronic components,” in Theory and Practice of Thermal Transient Testing of Electronic Components, M. Rencz, G. Farkas and A. Poppe, et al., Cham: Springer International Publishing, 2022, pp. 209–318. doi: 10.1007/978-3-030-86174-2_6.

9. ECPE Guideline AQG 324. “Qualification of power modules for use in power electronics converter units in motor vehicles.” Accessed: Nov. 15, 2024. [Online]. Available: https://www.ecpe.org/research/working-groups/ automotive-aqg-324

10. W. Zhao. “A star is born: Gallium Nitride and the coming age of compound semiconductors,” Semiconductor Engineering. Accessed: Nov. 15, 2024. [Online]. Available: https://semiengineering.com/a-star-is-born-galliumnitride- and-the-coming-age-of-compound-semiconductors/

11. A. Udabe, I. Baraia-Etxaburu and D. G. Diez. “Gallium Nitride Power Devices: A state of the art review,” IEEE Access, vol. 11, pp. 48628–48650, 2023, doi: 10.1109/ ACCESS.2023.3277200.

12. F. Roccaforte, G. Greco, P. Fiorenza, et al.. “An overview of normally-off GaN-based high electron mobility transistors,” Materials, vol. 12, no. 10, p. 1599, May 2019, doi: 10.3390/ma12101599.

13. S. She, et al.. “Thermal analysis and improvement of cascode GaN HEMT in stack-die structure,” in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA: IEEE, Sep. 2014, pp. 5709–5715. doi: 10.1109/ECCE.2014.6954184.

14. Y. Shan, W. Gao, Z. Huang, et al.. “Test methods and principles of thermal resistance for GaN HEMT power devices,” in 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China: IEEE, Aug. 2020, pp. 1–4. doi: 10.1109/ICEPT50128.2020. 9202571.

15. Z. Sarkany, et al.. “Thermal transient testing alternatives for the characterisation of GaN HEMT power devices,” in 2022 28th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Dublin, Ireland: IEEE, Sep. 2022, pp. 1–4. doi: 10.1109/THERMINIC57263. 2022.9950647.

16. G. Shengwei, F. Xiaoyu, S. Xingtao, et al.. “Investigation of switching characteristics degradation of GaN HEMT under power cycling aging,” IEEE Trans. Device Mater. Reliab., pp. 1–1, 2024, doi: 10.1109/TDMR.2024.3468013.

17. G. Farkas, T. Hara and M. Rencz. “Chapter 6: Thermal transient testing,” in Wide Bandgap Power Semiconductor Packaging, Elsevier, 2018, pp. 127–153. doi: 10.1016/B978-0-08-102094-4.00008-6.